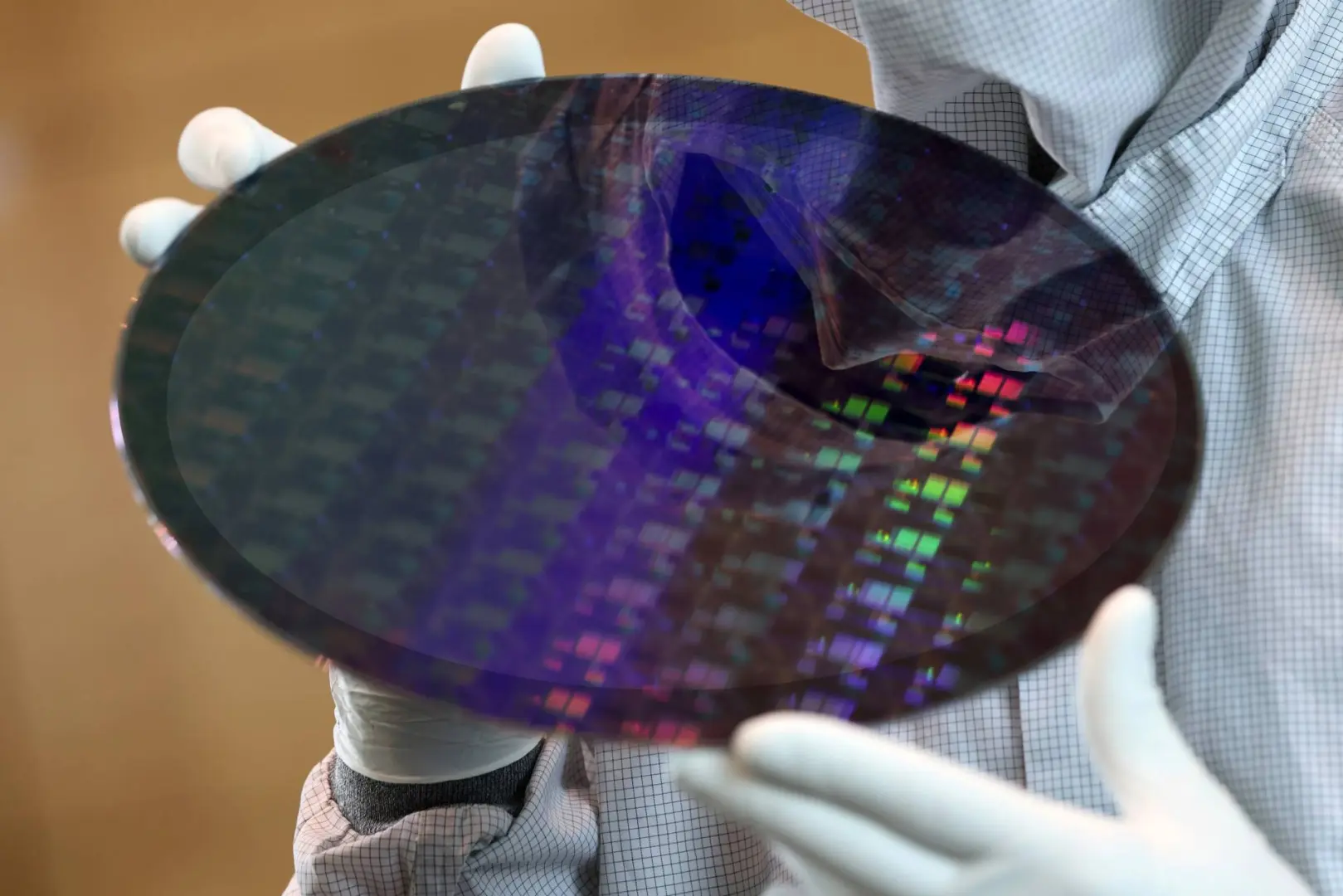

Dünyanın en büyük çip üreticilerinden biri olan Tayvan merkezli dev şirket, geleceğin çip üretim teknolojisi olarak görülen High-NA EUV litografi yöntemini A14 üretim sürecinde kullanmayacağını duyurdu. Bu kararın arkasında maliyet odaklı bir strateji yatıyor.

Genellikle yeni nesil yarı iletken teknolojilerinde öncü olan TSMC, A14 yongalarının üretiminde daha geleneksel sayılan 0.33-NA EUV teknolojisine güvenmeye devam edecek. Yapılan açıklamalara göre, şirketin bu kararı, High-NA EUV'nin beraberinde getirdiği yüksek maliyetler nedeniyle alındı. Sektördeki diğer oyuncular, özellikle Intel Foundry'nin bu yeni teknolojiye daha erken adapte olması beklenirken, TSMC'nin bu hamlesi dikkat çekiyor.

High-NA EUV teknolojisinin A14 üretim sürecinde kullanılmamasının temel nedeni, mevcut yöntemlere göre 2.5 kata kadar daha yüksek üretim maliyetleri yaratması. Bu durum, üretilecek yongaların fiyatını artırarak nihai tüketici ürünlerinde benimsenmesini zorlaştırabilir. TSMC, bunun yerine mevcut 0.33-NA EUV teknolojisiyle çoklu desenleme (multi-patterning) gibi teknikleri kullanarak aynı tasarım karmaşıklığını daha uygun maliyetlerle elde etmeyi hedefliyor.

High-NA EUV'nin yüksek maliyetine yol açan bir diğer faktör ise, çip tasarımının tek bir katmanı için birden fazla maske gerektirmesi. TSMC, bu son teknoloji aracı kullanmanın, belirgin bir performans artışı sağlamadan maliyetleri aşırı derecede yükselttiğini düşünüyor. Şirket, A14 sürecinde maliyet verimliliğine odaklanırken, High-NA EUV teknolojisini tamamen bir kenara atmış değil. Gelecekteki A14P gibi düğümlerde bu teknolojiyi kullanmayı planlıyor.

TSMC'nin bu erteleme kararı, özellikle Intel gibi rakiplerinin 18A gibi süreçlerde High-NA EUV'yi daha erken devreye alacak olması nedeniyle rekabet açısından önemli bir fark yaratabilir. Rakiplerine kıyasla High-NA EUV adaptasyonunda en az dört yıllık bir gecikme yaşayacak olan TSMC'nin bu stratejisinin sektördeki dengeleri nasıl etkileyeceği merak konusu.