Yarı iletken endüstrisindeki son gelişmeleri ve bu gelişmelerin TSMC'nin gelecek stratejisini nasıl etkilediğini anlamak amacıyla önemli bir görüşme gerçekleştirdik. TSMC'nin başkan yardımcılarından biri, şirketin teknoloji yol haritası, iş stratejisi ve önemli müşteri ilişkilerinden sorumlu.

TSMC, 1980'lerde kuruluşundan bu yana müşteri ihtiyaçlarını titizlikle karşılamayı ve sürekli gelişen yarı iletken ekosistemine uyum sağlamayı iş stratejisinin merkezine koydu. Önümüzdeki yıllarda müşteri gereksinimlerinin o kadar çeşitleneceği görülüyor ki, şirket farklı segmentlere özel ileri düzey üretim yetenekleri sunacak. Bu, TSMC'nin 'Herkesin Fabrikası' ideolojisinde büyük bir kilometre taşı olacak.

Herkesin Fabrikası Evriliyor

Geçmişte, PC'ler için işlemciler endüstrinin yeni nesil çip üretim teknolojilerine geçişinde itici güçtü. Ardından akıllı telefon devrimi oyunun kurallarını değiştirdi ve mobil yongalar (SoC), TSMC'nin (ve endüstrinin) ileri düzey üretim süreçlerinin ilk kullanıcıları haline geldi.

Yapay zekanın yükselişi bir kez daha her şeyi değiştiriyor; veri merkezi sınıfı işlemciler, TSMC'nin en ileri düğümlerini benimseyen kilit oyuncular olmaya hazırlanıyor. Ancak, tüketici cihazları her yıl daha fazla performans ve işlevsellik talep ettiği için, onlar da her yıl yeni bir işlem teknolojisi gerektiriyor. Sonuç olarak TSMC, birbirinden çok farklı ihtiyaçları karşılamak için farklı ileri düzey teknolojiler sunmak zorunda olduğu bir noktaya ulaştı. Bu durum, müşteri ve AI/HPC uygulamaları için gelişmiş paketleme teknolojileri sunmanın yanı sıra gerçekleşiyor.

Bunlar, TSMC'nin teknoloji yol haritası, iş stratejisi ve önemli müşteri ilişkilerinden sorumlu başkan yardımcısından öğrendiğimiz bazı önemli noktalar.

Önümüzdeki Yol

Kullanıcı ihtiyaçları değiştikçe, yarı iletken teknolojileri de buna ayak uyduruyor. Önümüzdeki yıllarda endüstri, genel olarak sözleşmeli çip üreticilerinden ve özellikle TSMC'den üç farklı ana yönelimde çözümler talep edecek:

- Maksimum transistör yoğunluğu ve performans verimliliği.

- Makul maliyetlerle en iyi güç dağılımı ile maksimum performans verimliliği.

- Veri merkezleri için çoklu çiplet (multi-chiplet) paketleme çözümleri.

Bu farklı talepleri karşılamak için TSMC, teknoloji yol haritasını üç tamamlayıcı yöne hizalıyor: gelişmiş transistör ölçeklendirme, optimize edilmiş güç dağıtımı ve çoklu çip sistem entegrasyonunda liderlik.

Akıllı telefonlar ve PC'ler gibi maksimum performans verimliliği gerektiren ürünler için TSMC, N3P, N2, N2P ve A14 işlem teknolojilerini sunacak. Bu düğümler, alan verimliliğinin ve pil ömrünün kritik olduğu mobil ve tüketici yongalarında verimli ölçeklendirme sağlayan, arka yüz güç dağıtımının karmaşıklığı ve maliyeti olmadan güçlü performans-watt başına optimizasyon sunar.

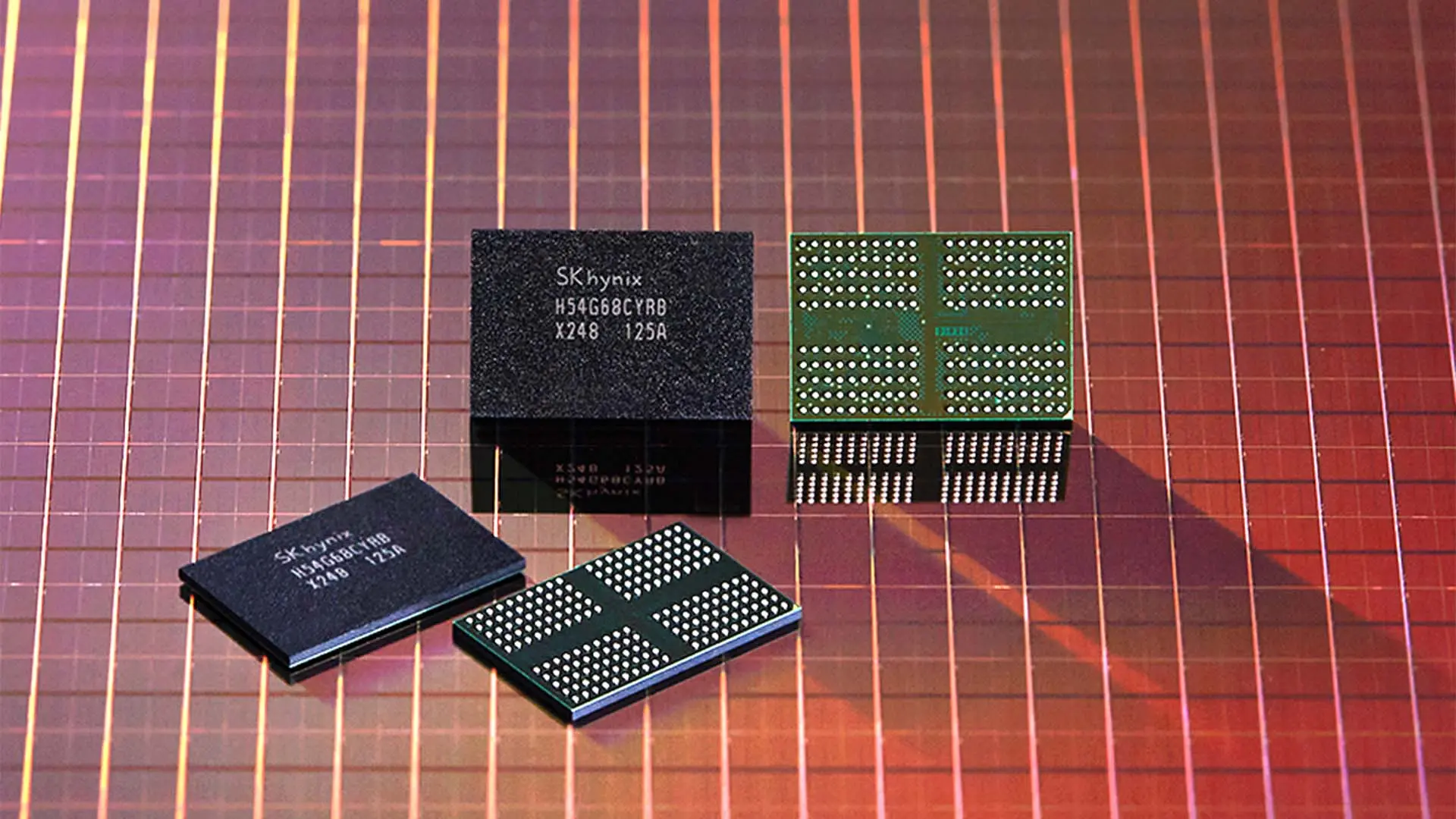

Kilowatt veya daha fazla güç tüketen veri merkezi işlemcileri için TSMC, 2026 sonlarında Süper Güç Raylı (Super Power Rail) Arka Yüz Güç Dağıtım Ağı (BSPDN) ile A16'yı ve ardından 2029'da SPR ile A14'ün bir versiyonunu sunmayı hedefliyor.

Ayrıca, veri merkezi sınıfı yapay zeka altyapısı için artan çoklu çiplet paketleme çözümleri ihtiyacını karşılamak amacıyla TSMC, silikon fotonik ve gömülü güç bileşenlerini kapsayan gelişmiş paketleme portföyünü genişleterek uyumlu, yüksek bant genişliğine sahip, enerji verimli sistemler oluşturuyor.

Moore Yasası Ölmedi (mi?)

Moore Yasası'nın hala geçerli olup olmadığı sıkça sorulan bir soru. N5'ten N3'e geçişte transistör yoğunluğunda yaklaşık %30 artış gördük. N3'ten N2'ye geçişte %15 transistör yoğunluğu artışı bekleniyor. A16 için beklenen artış %7 ila %10 arasında (A16'nın temel özelliği transistörlerden ziyade arka yüz güç dağıtımı). İleriye dönük her yeni düğümde ölçeklendirme (transistör yoğunluğu) söz konusu olduğunda azalan getiriler görmeye devam edecek miyiz, yoksa yeni çığırlar mı yaşanacak?

5nm'den 3nm'ye, 2nm'ye ve şimdi A14'e bakıldığında, şu anda gördüğümüz trend nesil başına yaklaşık %30 güç verimliliği artışı. Bu bir trend. Transistör yoğunluğunu nesil başına %20 civarında agresif bir şekilde artırmaya devam edebildiğimizi görüyoruz. Yani performans artışları %15 civarında. Bu rakamlar geçmiş nesillerle tutarlı. A14'ün ötesine baktığımızda, gördüklerimize dayanarak diyebilirim ki, birçok yenilik geliyor ve bu trendi A14'ün ötesinde de sürdürebileceğiz.

A14'ten bahsetmişken, bazı teknolojik atılımlar sayesinde tam düğüm ölçeklendirme faydaları sağladığını ve 2. Nesil GAA nanosheet transistörlerinden bahsettiğinizi söylediniz. Bu, atılımın yeni malzemeler gibi şeyleri mi içerdiği anlamına geliyor?

Şu noktada belirli bir yenilik planına girmek istemiyorum. Teknoloji ekibimiz gelecekte bir konferansta bir makale yayınlayabilir, bırakalım onlar konuşsun. Ancak size şunu söylemeliyim ki [N2/A16'dan] değişiklikler oldukça önemli. Bugün gördüklerimizden, A14'ü 2028'de önemli geometrik ölçeklendirme ile yüksek hacimli üretime sunma konusunda tam güvenimiz var. Dolayısıyla, bunun müşterilerin doğal teknoloji ölçeklendirme faydalarından gerçekten yararlanmalarını sağlayacağını düşünüyorum.

Her Uygulama Kendi Düğümünü İstiyor

A16'yı duyurduğunuzda, arka yüz güç dağıtımının özellikle AI/HPC tasarımları için faydalı olduğunu söylediniz. Bir röportajınızda, akıllı telefon yongalarının arka yüz güç dağıtımı olmayan işlem teknolojilerini kullanmaya devam edebileceğini belirttiniz. Müşterileriniz A14 ve A12 gibi yeni nesil düğümleri Arka Yüz Güç Dağıtım Ağı (BSPDN) olmadan kullanmaya devam edebilecekler mi?

Güç tüketiminin, bin veya binlerce watt tüketen yüksek performanslı bilgi işlem (HPC) işlemcilerine kıyasla o kadar önemli olmadığı mobil uygulamalar için bazı ayrışmalar görüyoruz. Mobil uygulama müşterilerinin güç, performans ve maliyet faydalarını elde etmek için ön yüz güç dağıtımına sahip olmayı sürdürmek istediğini düşünüyoruz. Bu yüzden N2 teknolojimizin, arka yüz güç dağıtımı veya Süper Güç Rayı (SPR) olmayan A14'ümüzün olduğunu görüyorsunuz.

Ama daha önce de bahsettiğim gibi, A14'ten bir yıl sonra HPC uygulamaları için Süper Güç Rayı ile [bu] teknolojinin bir versiyonuna sahip olacağız. Gözleminiz doğru, farklı ürün segmentlerinin kendi optimizasyon noktalarını elde etmelerini sağlamak için her iki teknoloji yolunu da sunacağız.

Bu, ileriye dönük olarak, işlem teknolojilerinizin belirli bir uygulamaya daha fazla mı uyarlanacağı anlamına geliyor?

Şöyle ifade edebilirsiniz: teknoloji platformumuz farklı uygulamalara göre uyarlanacak. Bu zaten bugün oluyor. Mobil için farklı bir optimizasyon noktamız olduğunu görüyorsunuz. Bu, tasarım sınıfı düzeyinde tüm seviyede gerçekleşiyor.

Örneğin transistör kütüphanesini görüyorsunuz. Farklı ürün yapılandırmaları, farklı ürün uygulamaları için optimize edilmiş farklı transistör kütüphanelerimiz var. Transistör teknolojisi düzeyinde, Süper Güç Rayı'ndan bahsediyorsunuz ve sonra paketlemeye baktığınızda, orada da farklı bir optimizasyon noktamız var. CoWoS'un büyük ölçüde HPC veya AI uygulamaları tarafından kullanıldığını görüyorsunuz. Ardından mobil müşteriler tarafından yoğun olarak kullanılan InFO [paketleme teknolojisine] bakıyorsunuz. Yani evet, teknolojimizi farklı ürün segmentleri için açıkça optimize ettik.

Eskiden, N4X, N3X ve şimdi N2X gibi HPC odaklı X işlem teknolojileri geliştiriyordunuz. Ancak A16'dan başlayarak, bunlar zaten başlangıçtan itibaren HPC için optimize edilmiş durumda, bu doğru mu?

Bu doğru. Süper Güç Raylı A16 gerçekten HPC uygulamaları için özel olarak tasarlandı. Ancak, X serisiyle - N4X, N3X ve N2X - müşterilerin tek iş parçacıklı uygulamalar için maksimum hızı elde etmelerini gerçekten sağlamaya çalıştık.

Not: TSMC, bir PDK içinde (örneğin, N5, N5P, N4, N4P veya N3B, N3E, N3P gibi) işlem teknolojilerinin birden çok yinelemesini sunma eğilimindedir. Bu, dökümhanenin pahalı ekipmanı mümkün olduğunca uzun süre kullanmasını ve ayrıca TSMC'nin müşterilerinin IP'lerini mümkün olduğunca uzun süre yeniden kullanmasını sağlar.

Bir düğümden diğerine geçiş daha pahalı hale geldiğine göre, bir nesil içindeki yineleme sayısının artmasını mı, yoksa üç veya dört civarında kalmasını mı bekliyorsunuz? A16 veya A14'ün özel versiyonları olacak mı?

Yol haritasına baktığınızda, tanıttığımız her ana düğümün kaç tane türev sürümü olduğunu sayabilirsiniz, değil mi? Yani 3nm örneğini kullandınız; N3E, N3X, N3P ve şimdi de N3C olduğunu zaten görüyorsunuz. Yani zaten dört farklı ana çeşidimiz var. Ama bir şeyi belirtmek istiyorum: bunlar [tek] bir teknolojinin farklı türev versiyonları, uyumlular. Örneğin, N3E'den N3P'ye ve N3C'ye, müşteriler tasarımın büyük bir kısmını yeniden kullanabilirler. Optimize ettiğimiz bazı şeyler nedeniyle çip tasarımını biraz farklı karakterize etmeniz gerekebilir. Ancak genel olarak, fiziksel tasarım doğrudan yeniden kullanılabilir. Bu, müşterilerimizin önceki ürün tasarımlarını veya önceki IP'lerini kullanarak işlem iyileştirmesine veya işlem optimizasyonuna dayalı daha fazla optimizasyon elde etmelerini sağlıyor.

Öyleyse, ileriye dönük olarak, A14 ve A16'dan başlayarak, bu özel versiyonları da sunmayı planlıyor musunuz?

Süper Güç Rayı oldukça yeni özellikler sunuyor çünkü güç bağlantısı tamamen ön yüzden arkaya taşındı. Dolayısıyla, oldukça önemli bir yeni tasarım gerektiriyor. Bu A16'nın benzersizliğidir. Gücü wafer'ın arka yüzüne taşıdığınızda, ön yüzdeki hücre kütüphanesinin büyük bir kısmı, bazı minimum değişiklikler uygulayarak yeniden kullanılabilir. Değişiklikler büyük ölçüde gücü nasıl bağladığınızda gerçekleşir.

Ancak yepyeni bir düğüm olan A14'ten başlayarak, bu teknolojinin bugün yaptığınız gibi başka yinelemelerini sunmayı planlıyor musunuz?

Size şunu söyleyebilirim ki, önceki nesillerde, 2nm gibi, A14 ile de yaptıklarımızı takip etmeye devam ediyoruz. Gelecek yıl A14P veya A14X hakkında konuşursak şaşırmam. Bir noktada A14C de olacak. Bunların hepsi, uyumlu, artımlı hale getirme ve müşterilerimizin 14A'ya geçiş yaptıklarında yaptıkları yatırımın faydasını toplamalarını sağlama gibi benzer bir felsefeyi takip edecek.

İşlem teknolojisinin C varyantlarından bahsetmişken, N3C'nin maliyet faydalarını tahmin edebilir misiniz?

Ürün düzeyindeki maliyet faydası belirli ürün tasarımına, ürün yapılandırmasına bağlıdır, ancak tamamen doğal teknoloji yeteneği açısından bakıldığında, yaklaşık %10'luk bir maliyet faydasından bahsediyorum.

Gereksinimler Arttıkça, Çip Tasarımcıları Daha Gelişmiş İşlem Teknolojilerini Benimser

TSMC yönetimi, müşterilerin tamamen yeni IP'leri GAA işlem düğümleri için benimsemek zorunda kalmasına rağmen, N2'nin ilk iki yıldaki bant sayısı sayısının N3 ve N5'in ilk iki yıldaki bant sayısı sayısından daha yüksek olmasının beklendiğini birkaç kez belirtti. Bunun nedenleri nelerdir?

Ana nedenin uygulamadan kaynaklandığını düşünüyorum. Bugünlerde yapay zeka hakkında çok konuşuyoruz. Ama yapay zekanın temel gereksinimi aslında enerji verimli hesaplama, değil mi? İster veri merkezi olsun, ister uç cihazlar olsun. Ama veri merkezini düşünün, değil mi? Bugün veri merkezinin en büyük tek maliyet bileşeni elektrik, tüketilen güç. Dolayısıyla daha gelişmiş silikon teknolojisi benimseyerek gücü önemli ölçüde düşürüyorsunuz.

Bu nedenle müşteri, daha gelişmiş silikon teknolojisini benimseyerek önemli bir sahip olma maliyeti faydası görüyor. Bu, müşterilerin gelişmiş silikon teknolojisi düğümlerini benimsemede daha agresif olmalarının temel nedenidir. Aynı şey, daha fazla hesaplama yeteneği dahil etmeye devam ettikçe de geçerli.

Yapay zeka yeteneğini düşünün, örneğin bir video için. Aldığınız ve yüklediğiniz video, kapsamlı bir hesaplama yeteneği gerektirir. Dolayısıyla, bunların hepsi temel olarak müşteriyi daha gelişmiş bir silikona, daha gelişmiş transistör teknolojisine gitmeye yönlendiriyor.

Bu nedenle, trendin aslında hızlandığını görüyoruz. Bu yüzden daha önce o tabloyu gösterdim. Son üç nesilde, NTO (Yeni Bant Çıkışı) sayısının artmaya devam ettiğini görüyorsunuz, değil mi? İlk yıl için 2 kat, ikinci yıl için 4 kat. İşte bu sayıların arkasındaki neden bu.

Veri merkezi uygulamaları giderek artan bir şekilde çoklu çiplet tasarım yaklaşımını kullanıyor. Ancak çoklu çiplet çözümleri söz konusu olduğunda, bir çip tasarımı ayrıştırıldığında güç tüketiminin arttığını biliyoruz, bu yüzden çip tasarımcıları bununla uğraşmak zorunda kalıyor. Ancak dökümhane düzeyinde ayrıştırılmış tasarımlarının güç tüketimini azaltmalarına yardımcı olabileceğinizi düşünüyor musunuz?

Bu zaten bugün oluyor. Her belirli işlev, element, CPU, GPU, yapay zeka sinir motoru gibi. Bunlar aslında farklı bir optimizasyon noktası gerektiriyor. Bugün, aynı kalıpta farklı işlev tasarım optimizasyon noktaları için farklı bir transistör kullanılmasına izin veren birçok farklı transistör çeşidi sunuyoruz. Bunu zaten yapıyorlar. Müşteriyle birlikte çalışarak bu belirli optimizasyonu sağlamak bizim için çok önemli. Yani bu monolitik bir tasarım.

Çoklu çiplet tasarımında ise, kökten farklı silikon teknolojisi kullanabilirler. Örneğin, bazıları hesaplama için en gelişmiş teknolojiyi, diyelim ki 2nm'yi kullanır, ancak düşük güç, düşük hızlı elementler için 3nm veya hatta 5nm veya 4nm'de kalabilirler ve ardından gelişmiş entegrasyon şemamızı kullanarak bunları bir araya getirebilirler. Dolayısıyla bu zaten bugün oluyor, sistem düzeyinde farklı ürün uygulamaları için farklı müşterilerimizle çok yakın çalışıyoruz.

Not: Farklı transistör kütüphaneleri ve işlem teknolojilerinin kullanılması güç tüketimini optimize edebilir. Ancak, çoklu çiplet çözümü yine de entegre bir çözüme göre muhtemelen daha fazla güç tüketecektir. 3D entegrasyon söz konusu olduğunda, TSMC müşterileri bu düğümün temel bir kalıp olarak kullanılabilmesi için dökümhanenin bir işlem teknolojisinin TSV versiyonlarını (örneğin, N4 TSV, N3 TSV, N2 TSV vb.) geliştirmesini beklemek zorundadır.

Geçen yıl, son derece güçlü çözümler için wafer-level entegrasyonundan bahsettiniz. Ama kaç müşteri aslında bu kadar büyük wafer-level işlemcilerle ilgileniyor?

Bu trendi görüyoruz, insanlar daha fazla hesaplama birimini, daha fazla HBM'i bir araya getirmek için daha büyük interposer boyutunu artırmaya devam ediyor. Dolayısıyla bu trend devam edecek. Müşterilerin gelecekteki ihtiyaçlarını karşılamak için wafer-level entegrasyonundan yararlanmak istediğini görüyoruz. Ama biliyorsunuz, bu muhtemelen birkaç yıl uzakta çünkü şu anda üretim CoWoS'tan bahsediyorum, 3.5X reticle boyutunda, gelecekte 5X reticle boyutu ve 9X reticle boyutu olacak ve 9X'in ötesinde, wafer-level entegrasyonu önemli bir entegrasyon şeması haline gelecek. Ancak bunlar hala birkaç yıl uzakta. Ama müşteriler var. Bunlar wafer-level entegrasyonundan daha agresif bir şekilde yararlanıyorlar.

TSMC Gelişmeye Devam Edecek

Farklı pazar segmentlerinden 500'den fazla müşterisi bulunan TSMC, artan farklı müşteri ihtiyaçlarını karşılamak için stratejisini geliştiriyor; AI, HPC ve tüketici uygulamaları için birden çok, segmente özel optimize edilmiş ileri düzey üretim teknolojisi sunuyor ve müşterilerinin üretim süreçleri evrildikçe IP'lerini yeniden kullanmalarını sağlıyor. Bu, şirketin uzun süredir devam eden 'Herkesin Fabrikası' felsefesini bir kez daha vurguluyor ve 'tek beden herkese uyar' yaklaşımından, amaca yönelik düğümler ve paketleme çözümleri portföyüne doğru bir kayma gösteriyor.

İleriye dönük olarak TSMC, AI ve HPC uygulamaları için Süper Güç Raylı arka yüz güç dağıtım ağı (örneğin, A16 ve A14P) ile ileri düzey işlem teknolojileri; istemci ve akıllı telefon işlemcileri için BSPDN olmayan ileri düzey düğümler (örneğin, N3P, N2, N2P, A14); ve maliyete duyarlı uygulamalar için tasarımlar için maliyet optimize edilmiş gelişmiş düğümler (örneğin, N4C, N3C, N2C) sunacak.

Daha önce şirket, maliyet optimize edilmiş düğümlerini yalnızca olgun düğümler için sunuyordu (örneğin, N16FFC, N12FFC). Çoklu çiplet ve ayrıştırılmış tasarımlar için TSMC, müşteri/mobil (InFO), AI ve HPC 2.5D entegrasyonu (CoWoS), müşteri ve veri merkezi 3D entegrasyonu (SoIC) ve hatta en zorlu çözümler için wafer-level sistem (SoW) entegrasyonu dahil olmak üzere çeşitli tekliflerle 3DFabric portföyünü genişletmeye devam ediyor.