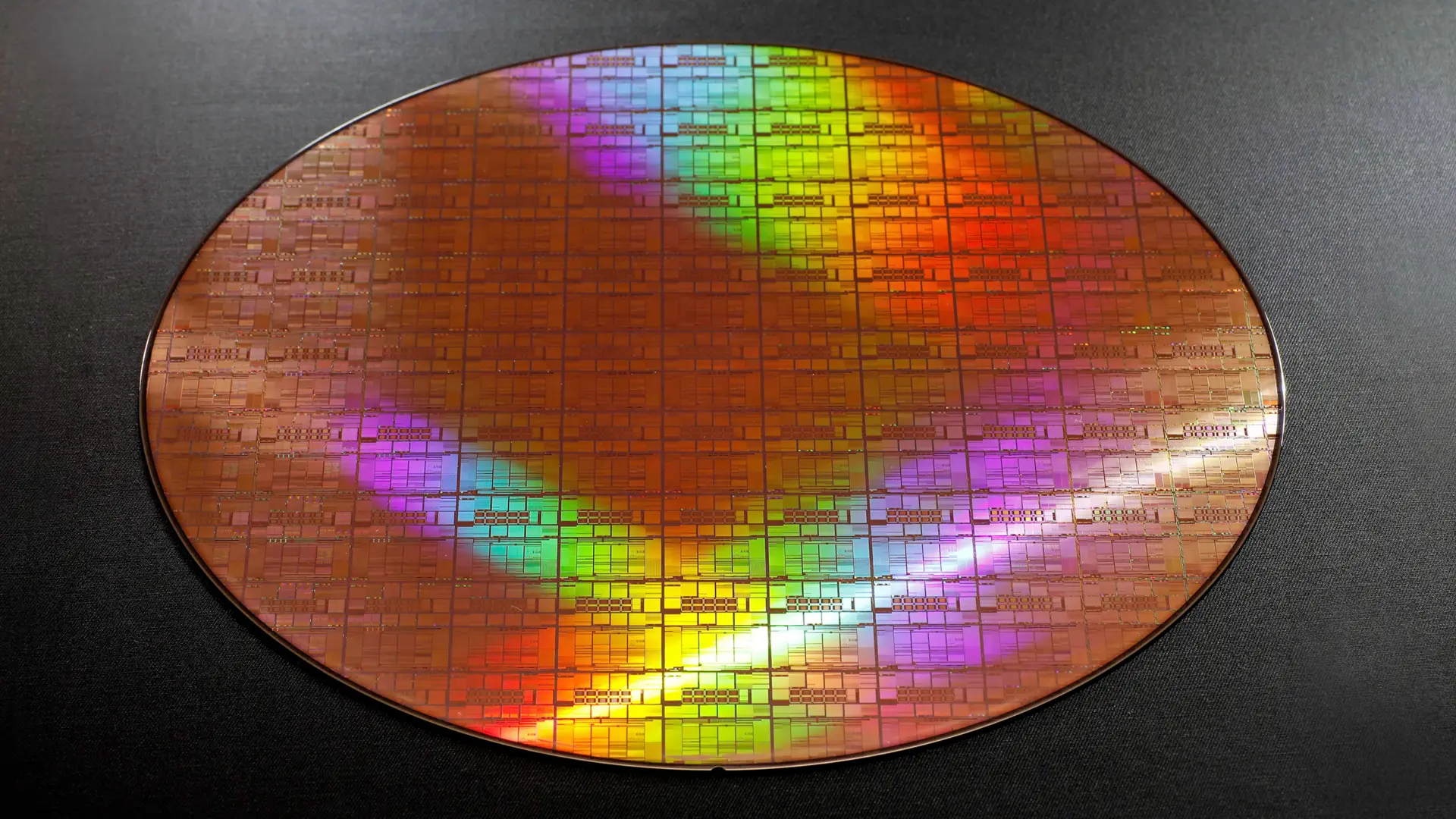

Japon yarı iletken üreticisi Rapidus, 2 nanometre (nm) teknolojiyle Gate-All-Around (GAA) transistör yapılarının ilk test üretimlerini IIM-1 tesisinde başarıyla başlattığını duyurdu. Şirketten yapılan açıklamada, ilk test waflerlerinin hedeflenen elektriksel özelliklere ulaştığı ve bu durumun fabrika ekipmanlarının planlandığı gibi çalıştığını ve süreç teknolojisi geliştirmenin sorunsuz ilerlediğini gösterdiği belirtildi.

Test Waferleri Fabrika İçinde İlerliyor

Prototipleme, yeni bir teknolojiyle üretilen ilk test devrelerinin güvenilir, verimli bir şekilde çalışıp performans hedeflerini karşıladığını doğrulamak için yarı iletken üretiminde kritik bir kilometre taşıdır. Rapidus, şu anki aşamada test devrelerinin eşik gerilimi (transistörün iletime geçtiği voltaj), iletim akımı (açıkken geçirebildiği akım miktarı), kaçak akım (kapalıyken istenmeyen akış) ve alt eşik eğimi (cihazın kapalıdan açığa ne kadar keskin geçtiği) gibi elektriksel özelliklerini ölçüyor. Ayrıca anahtarlama hızı, güç tüketimi ve kapasitans gibi diğer önemli özellikler de değerlendiriliyor. Rapidus sonuçları gizli tutsa da, test waferlerinin fabrika ortamında işleniyor olması, sürecin ilerlemesi açısından önemli bir gelişme olarak kabul ediliyor.

IIM-1 tesisi, Eylül 2023'te başlayan inşaatından bu yana hızlı bir gelişim gösterdi. Temiz oda 2024'te tamamlandı ve Haziran 2025'e kadar gelişmiş DUV ve EUV litografi araçları dahil olmak üzere 200'den fazla ekipman kuruldu. Rapidus, Aralık 2024'te gelişmiş EUV araçlarını kurdu ve Nisan 2025'e kadar ilk başarılı pozlamalarını tamamladı. Fabrika artık test waferlarını işleyebilecek olgunluğa ulaşarak, Rapidus'un GAA devrelerinin elektriksel özelliklerini ölçmesine, olası süreç sorunlarını belirlemesine ve ekipman ayarlarını veya üretim adımlarını hassaslaştırmasına olanak tanıyor.

Tüm Adımlar İçin Tek Wafer İşleme

Rapidus'un basın bülteninde dikkat çeken bir nokta, IIM-1 fabrikasında ön uç süreç adımlarının tamamında “tek wafer işleme” yaklaşımının kullanılacak olmasıdır. Bu yöntem, her bir wafer’ın toplu işlenmek yerine bireysel olarak ele alınması, işlenmesi ve denetlenmesi prensibine dayanır.

Günümüzde Intel, Samsung ve TSMC gibi büyük çip üreticileri, yarı iletken üretim süreçlerinde toplu ve tek wafer işleme yöntemlerini bir arada kullanıyor. EUV ve DUV desenleme, plazma aşındırma, atom katmanı biriktirme veya kusur izleme gibi hassasiyet gerektiren kritik adımlar için tek wafer işleme tercih edilirken; oksidasyon, iyon implantasyonu, temizleme ve tavlama gibi diğer adımlar için waferler toplu olarak işleniyor.

Rapidus ise oksidasyon, iyon implantasyonu, desenleme, biriktirme, aşındırma, temizleme, tavlama gibi tüm süreç adımlarına tek wafer yaklaşımını uygulamayı planlıyor. Rapidus'a göre bu yaklaşım, her bir operasyon üzerinde hassas bir kontrol sağlayarak, o tek wafer üzerindeki gözlemlenen koşullara veya sonuçlara özel ayarlamalar yapılmasına imkan tanıyor. Her wafer bağımsız olarak işlem gördüğünden, mühendisler parametreleri gerçek zamanlı olarak hassaslaştırabilir, anormallikleri erken tespit edebilir ve tüm bir grubun tamamlanmasını beklemeden hızlı düzeltmeler uygulayabilir. Bu yöntemin bir diğer avantajı ise, diğer çip üreticilerinin kullandığı karma yöntemlere kıyasla wafer başına daha fazla miktarda yüksek çözünürlüklü veri üretmesidir. Bu veriler, üretim koşullarını izleyen ve optimize eden yapay zeka algoritmalarını beslemek için kullanılabilir. Bu algoritmalar, kusur yoğunluğunu azaltmak ve verimliliği artırmak için sürekli süreç iyileştirmeleri (CPI) ve performans varyasyonlarını azaltmak için istatistiksel süreç kontrolü (SPC) için daha hızlı bilgi toplama olanağı sunabilir. Ayrıca, tek wafer işleme sistemleri ayarları değiştirmeyi ve küçük ve büyük üretim döngüleri arasında geçiş yapmayı kolaylaştırır; bu da daha küçük ölçekli üreticilere hizmet etmeyi hedefleyen Rapidus için önemli bir avantajdır.

Ancak bu yöntem bazı ödünleşmeleri de beraberinde getiriyor. Waferler birer birer işlendiği için, alet başına verimlilik (bazı aletler için) toplu işlemeye kıyasla daha düşüktür, bu da üretim döngü sürelerini uzatabilir ve üretimi daha maliyetli hale getirebilir. Gereken ekipmanlar daha karmaşık ve maliyetlidir ve waferların tüm adımlar boyunca bireysel olarak hareketinin koordinasyonu ek yük getirir.

Rapidus, daha yüksek başlangıç maliyetleri ve daha yavaş işlem sürelerine rağmen, tek wafer işlemenin kusur azaltma, verimlilik artışı ve uyarlanabilir süreç kontrolü gibi uzun vadeli faydalarının, 2 nm ve ötesi çiplerin üretimi için çekici bir strateji olabileceğine inanıyor.

PDK, 2026'nın İlk Çeyreği Hedefinde

Rapidus, erken müşterileri desteklemek amacıyla süreç geliştirme kitinin (PDK) ilk versiyonunu 2026'nın ilk çeyreğinde yayınlamaya hazırlanıyor. Şirket ayrıca IIM-1 sitesinde müşteri çip tasarımı prototiplemesi için gerekli altyapıyı sağlamak üzere de çalışmalarını sürdürüyor.