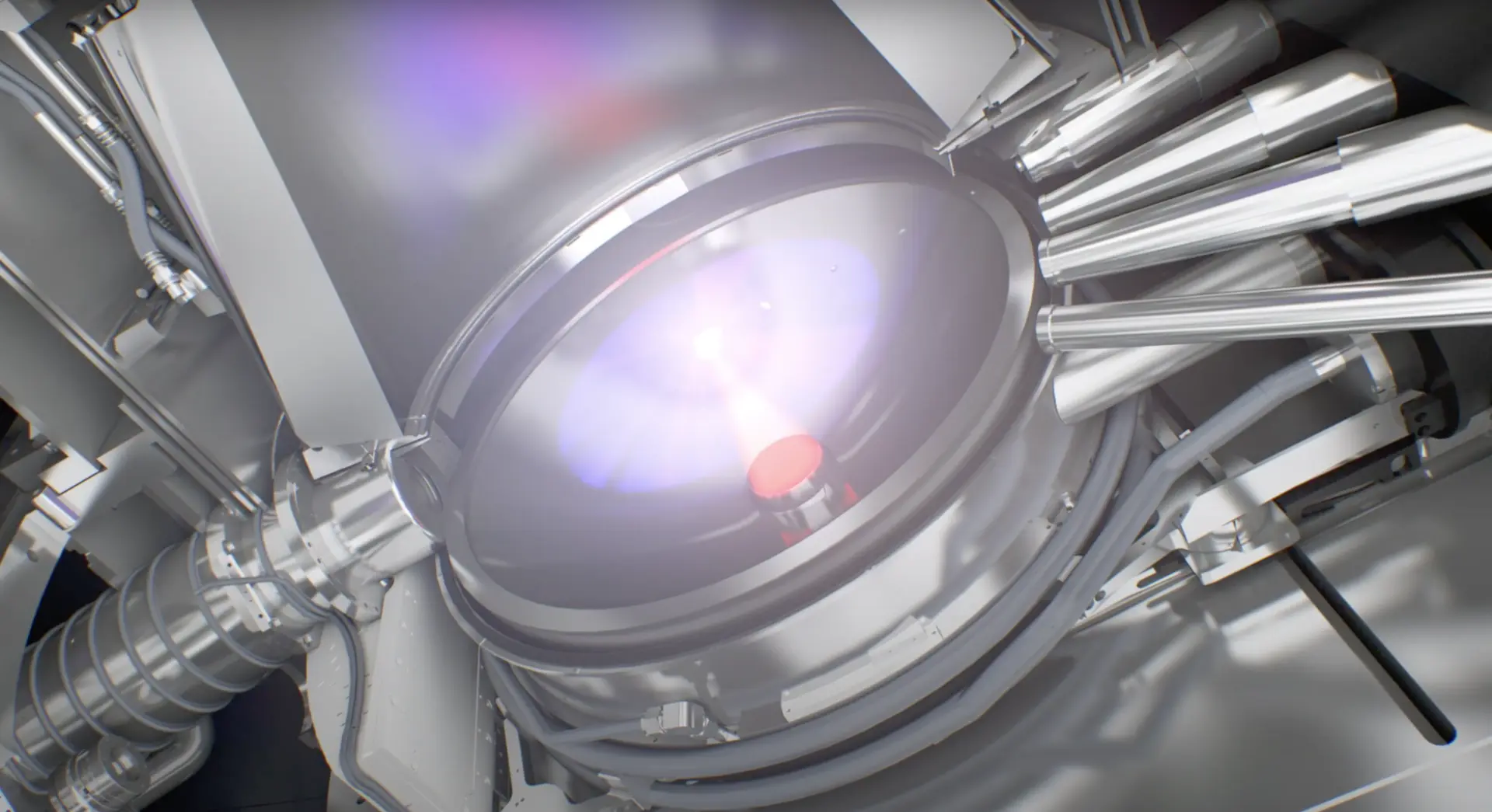

Geleceğin gelişmiş çip tasarımlarının üretiminde, ultra gelişmiş litografi makinelerinin rolünün eskiye kıyasla daha az kritik hale gelebileceği iddia edildi. Yarı iletken endüstrisinin bel kemiği olarak kabul edilen ASML firmasının ürettiği ekstrem ultraviyole (EUV) litografi makineleri, günümüzdeki en ileri çiplerin üretiminde (TSMC gibi firmaların çok küçük devreleri silikon plakalara aktarmasını sağlayarak) kilit bir rol oynuyor.

Ancak, bir Intel yöneticisine göre, gelecekteki transistör tasarımları – özellikle Gate-All-Around FET (GAAFET) ve Complementary FET (CFET) gibi yenilikler – üretim sürecinde litografi sonrası adımlara, yani daha çok 'kazıma' (etching) teknolojilerine dayanacak ve bu durum litografinin genel önemini azaltacak.

Intel Yöneticisi: Kazıma Şirketleri Gelecekte Daha Büyük Rol Oynayabilir

Bir platformda yapılan bir tartışmada görüşlerini paylaşan adı açıklanmayan Intel yöneticisi, geleceğin transistör tasarımlarının ileri litografi ekipmanlarına daha az, kazıma teknolojisine ise daha fazla bağımlı olacağını belirtti. ASML'nin ileri EUV ve yüksek-NA EUV tarayıcıları gibi litografi makineleri, özellikle ihracat kısıtlamaları nedeniyle en çok konuşulan çip üretim ekipmanları olsa da, bir çipin üretimi litografiden ibaret değildir.

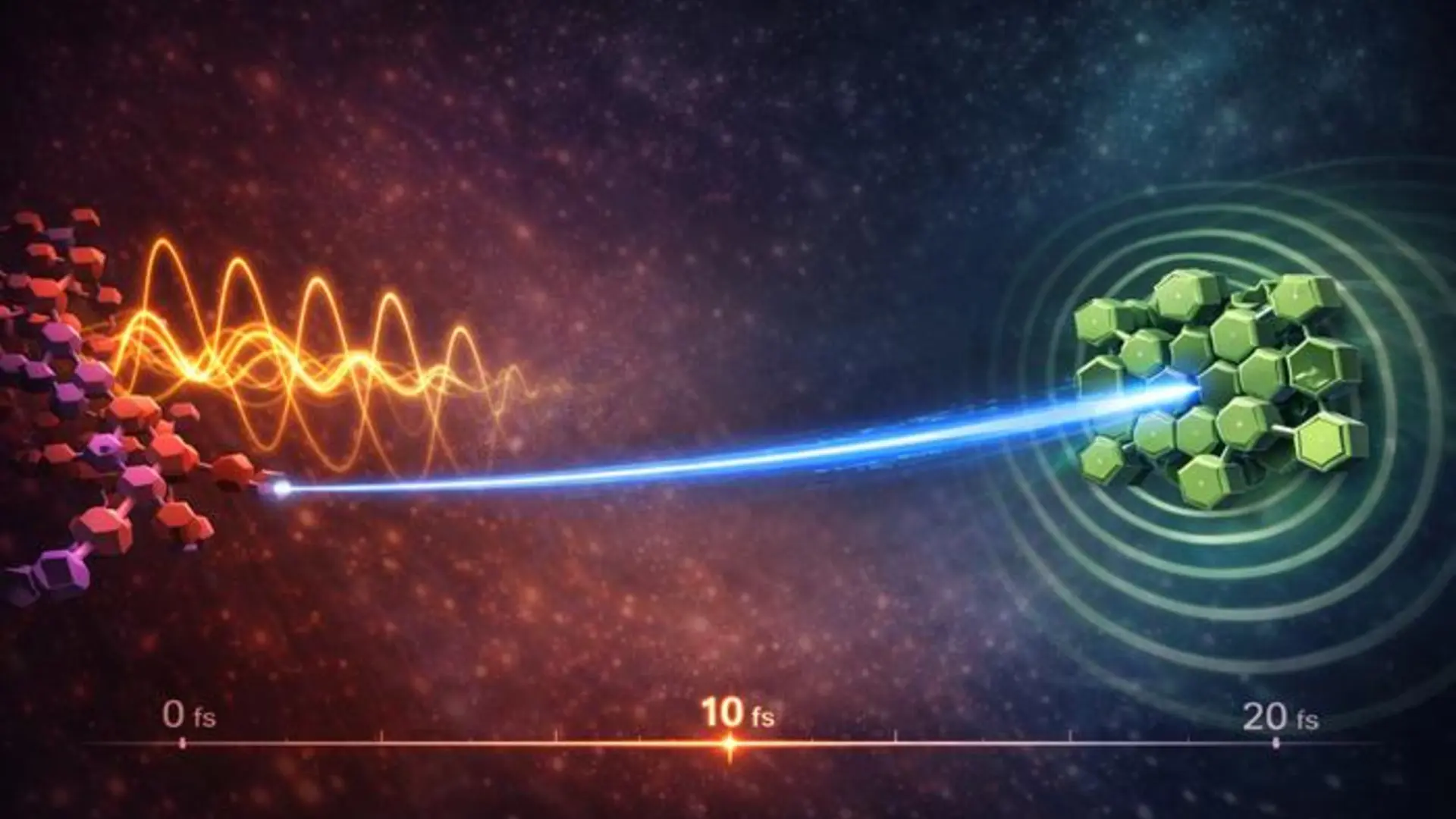

Litografi, üretim sürecinin ilk adımıdır ve devre desenlerini silikon plaka üzerine aktarır. Bu desenler daha sonra biriktirme (deposition) ve kazıma (etching) gibi işlemlerle nihai hale getirilir. Biriktirme, plaka üzerine malzeme eklenmesini sağlarken, kazıma ise istenmeyen malzemeyi seçici olarak kaldırarak transistör ve devre desenlerini oluşturur.

Intel yöneticisine göre, GAAFET ve CFET gibi yeni transistör tasarımları, çip üretim sürecinde litografi makinelerinin önemini azaltabilir. Özellikle EUV tarayıcıları, 7 nanometre ve daha ileri teknolojilerdeki çipleri üretmede (küçük devre desenlerini plaka üzerine aktarabilme yetenekleri sayesinde) kritik bir rol oynamıştır.

Desenler aktarıldıktan sonra, kazıma işlemi plaka üzerindeki fazla malzemeyi kaldırarak desenleri sonlandırır. Mevcut transistör tasarımlarının çoğu, transistörlerin alt kısımdan yalıtım malzemesine bağlandığı ve içlerindeki elektrik akışını kontrol eden bir 'geçit'ten geçtiği FinFET modelini takip eder. GAAFET gibi daha yeni tasarımlar, geçidi transistörlerin etrafına tamamen sarar ve transistör gruplarını paralel yerleştirir. CFET gibi ultra ileri tasarımlar ise transistör gruplarını üst üste yığarak plaka üzerindeki alandan tasarruf sağlar.

Intel yöneticisine göre, GAAFET ve CFET tasarımları geçidi her taraftan 'sardığı' için, plaka üzerindeki fazla malzemenin hassas bir şekilde kaldırılması hayati önem taşıyor. Bu 'sarılma', çip üreticilerinin malzemeyi yanal (yanlardan) olarak kaldırmasını gerektiriyor. Bu da, en küçük devre boyutlarını elde etmek için plakanın litografi makinesinde geçirdiği süreyi artırmak yerine, üreticilerin odağının malzemeyi kazıma yoluyla kaldırmaya kayacağı anlamına geliyor.

Çip üretiminde 'yanal' yönün artan önemi, yüksek-NA EUV makinelerinin, öncülleri olan EUV tarayıcılarının 7 nanometre veya daha ileri teknolojilerdeki çipleri üretmek için olduğu kadar 'kritik' olma ihtimalinin daha düşük olduğu anlamına geliyor. Bu kaymanın nihai sonucu ise, yalnızca belirli bir düzlemde değil, dikey olarak da yüksek yoğunluk elde edilebildiği için 'minimum özellik boyutuna olan bağımlılığın azalması' şeklinde değerlendiriliyor.