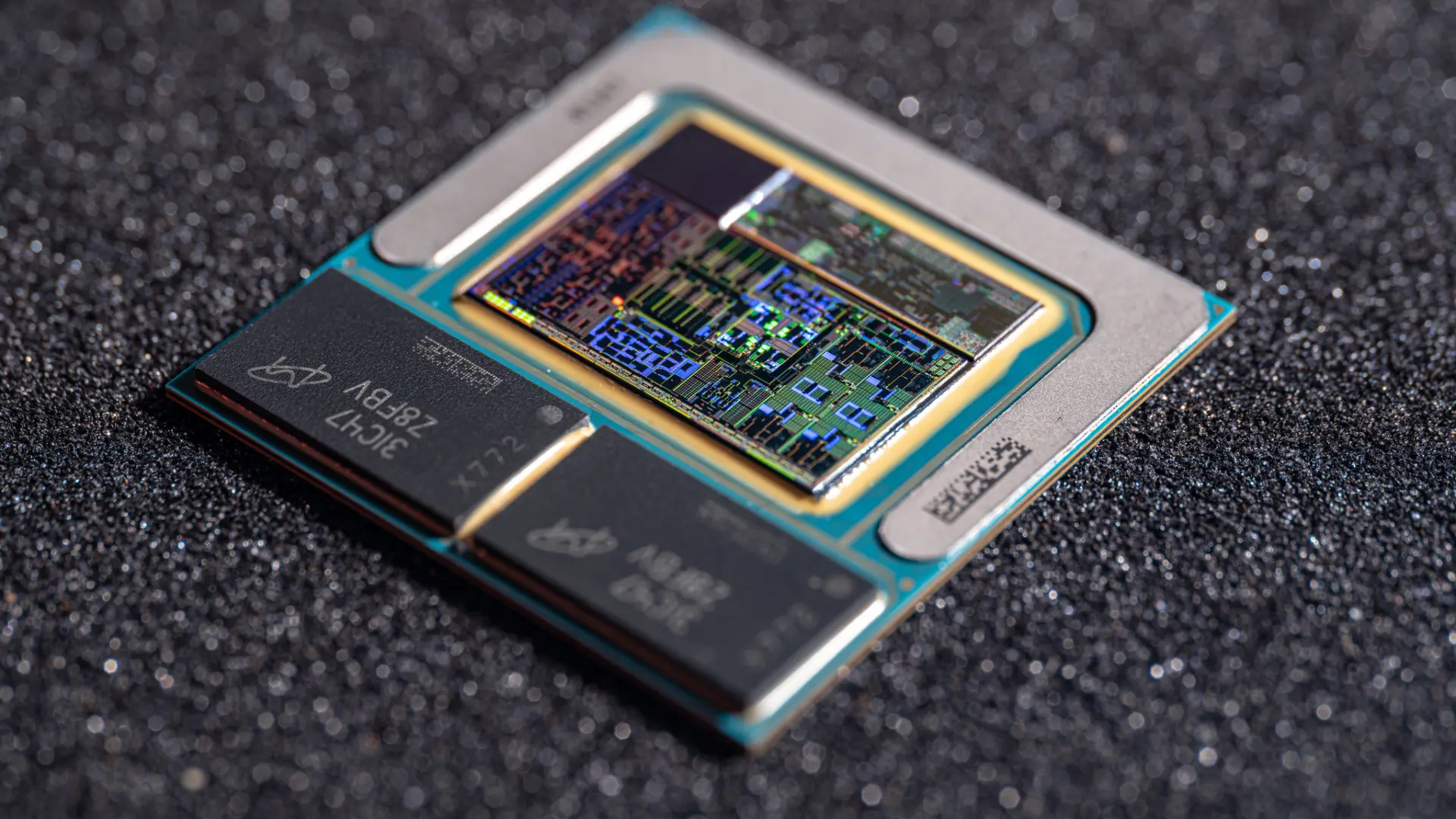

Intel'in Lunar Lake işlemcileri, Arm tabanlı SoC'lerde görmeye alıştığımız ultra verimli tasarımı x86 mimarisinin köklü temeliyle birleştirerek pazarda dikkat çekmişti. Donanım dünyasında yüksek çözünürlüklü işlemci kalıp (die) görüntüleri yakalamasıyla tanınan bir meraklının paylaştığı yeni detaylı görseller, Lunar Lake örneklerinin iç yapısını ve Intel'in titiz mühendisliğini gözler önüne seriyor.

Lunar Lake'in geliştirilmesi, Intel için maliyet ve ürün kalitesi arasında stratejik bir denge kurma zorunluluğunu beraberinde getirdi. Sonuç, Arm tabanlı alternatiflere oldukça benzeyen bir yapı sunarken, performans tarafında rekabetçi kalabilen bir işlemci oldu. Ancak inovasyonun bir bedeli var; Lunar Lake ile güçlendirilen dizüstü bilgisayarlar genellikle üst fiyat segmentinde yer alıyor. Hatta eski Intel CEO'su tarafından da "bir kerelik" bir tasarım olarak nitelendirilen Lunar Lake'in, sızan yol haritalarında bir devam modelinin görülmemesi de bu durumu destekliyor.

Lunar Lake, Arrow Lake ile aynı temel mikro mimariyi ve üretim sürecini paylaşsa da, Intel tamamen farklı bir geliştirme yaklaşımı izledi. TSMC'nin N3B sürecinde üretilen Hesaplama Çipi (Compute Tile), 12 MB paylaşımlı L3 önbelleğe sahip dört adet Lion Cove tabanlı Performans (P) çekirdeği ve her bir P çekirdeği için 2.5 MB özel L2 önbellek barındırıyor. Arrow Lake'in aksine, Skymont tabanlı verimlilik çekirdeği kümesi (E) aynı L3 önbellek havuzunu paylaşmıyor; bunun yerine kendi özel 4 MB L2 önbelleğine sahip bir "Düşük Güç Adası" üzerinde yer alıyor. E-çekirdeklerinin yanında ise yaklaşık 48 TOPS yapay zeka performansı sunduğu düşünülen altı NCE'ye (Neural Compute Engines) sahip NPU (Sinirsel İşlem Birimi) bulunuyor.

Hesaplama Çipi ayrıca sekiz adede kadar Xe2-LPG çekirdeği içeren Battlemage tabanlı entegre GPU'ya ve Medya Motoru'na ev sahipliği yapıyor. Intel, tüm temel işlem bileşenlerini tek bir çiplete sığdırarak, çipletler arası iletişimin gecikmesini ve güç tüketimini önemli ölçüde azalttı. Intel ayrıca, Arm SoC'lerinde görülenlere benzer şekilde, bellek denetleyicisinin yanında CPU çekirdekleri, entegre GPU, NPU ve Medya Motorları arasında paylaşılan 8 MB'lık bir Sistem Seviyesi Önbellek (SLC) içeriyor. Entegrasyonu daha da sıkılaştırmak ve gecikmeyi azaltmak için, bellek fiziksel katmanı, SoC'nin ana belleği olarak görev yapan, doğrudan paket üzerine lehimlenmiş ve yükseltilemeyen (16 GB veya 32 GB) iki adet LPDDR5x-8533 belleğin hemen altında, Hesaplama Çipi'nin tam üzerinde konumlandırılmış.

Hesaplama Çipi'nin altında, TSMC'nin N6 sürecini kullanan Platform Denetleyici Çipi (Platform Controller Tile) ve yapısal sağlamlık için eklenen bir boş çiplet yer alıyor. Platform Denetleyici Çipi, Arrow Lake'deki G/Ç Genişletici Çipi olarak düşünülebilir. Bu çiplet, USB, Thunderbolt ve PCIe 4.0/5.0 arayüzlerinin yanı sıra Bluetooth ve Wi-Fi bağlantısı gibi önemli yüksek ve düşük hızlı G/Ç bileşenlerini barındırıyor. Tüm bu çipletler, Intel'in Foveros 3D paketleme teknolojisi aracılığıyla bağlanan 22FFL tabanlı aktif bir ara bağlantı katmanı (active interposer) üzerine yerleştirilmiş.

Bunlar sadece çipin genel teknik özellikleri; tam yerleşim düzeni farklılık gösterebilir, çünkü Intel'in tüm bu bileşenleri tam olarak nasıl yerleştirdiğini bir mühendisin yardımı olmadan kesin olarak bilmek mümkün değil. Ortaya çıkan detaylı görüntüler üzerine yapılan yorumlar ve işaretlemeler, genellikle görsel ipuçlarına dayanır ve farklı analistler farklı yorumlar sunabilir.