Google'ın merakla beklenen yeni nesil işlemcisi Ironwood TPU v7, yapay zeka alanında çığır açmaya hazırlanıyor. NVIDIA'nın güçlü Blackwell GPU'larına rakip olarak gösterilen bu özel entegre devre (ASIC), Google'ın TPU tasarım süreçleri ve teknoloji ortağı MediaTek'in bu alandaki deneyimini mobil çiplere taşıyacağına dair umutları artırdı. Bu gelişmelerin ilk meyvesi olarak, MediaTek'in önümüzdeki Dimensity 9600 yonga setinde önemli verimlilik artışları bekleniyor.

Google Ironwood TPU v7 ve MediaTek'in Rolü

Google'ın Ironwood TPU v7 yonga setinin mimarisi hakkında şu bilgiler mevcut:

- Her biri şu bileşenleri içeren çift çiplet tasarımına sahip:

- Yapay zeka iş yüklerinin temelini oluşturan matris çarpımı işlemlerini yüksek verimlilikle gerçekleştiren Tensör Çekirdekleri (TensorCore). Bu çekirdekler, yüksek bant genişlikli bellek (HBM) ihtiyacını azaltarak işlem süreçlerini hızlandırıyor.

- Vektör İşlem Birimi (VPU): Aktivasyon fonksiyonları (ReLU gibi) ve normalizasyonlar gibi yapay zeka modelleri için gerekli genel amaçlı, öğe bazlı işlemleri yönetir.

- Matris Çarpım Birimi (MXU): Matris çarpımı işlemlerini gerçekleştirir.

- Düzensiz, veriye bağlı bellek erişimi gerektiren kullanım durumlarını verimli bir şekilde yöneten 2 adet SparseCore. Bunlar, özellikle büyük kategorik özellik değerlerini daha küçük, yoğun vektör temsillerine dönüştürerek birçok yapay zeka operasyonunda kritik bir adım olan gömme (embedding) işlemlerini ele alır.

- 96 GB yüksek bant genişlikli bellek (HBM).

- Yapay zeka iş yüklerinin temelini oluşturan matris çarpımı işlemlerini yüksek verimlilikle gerçekleştiren Tensör Çekirdekleri (TensorCore). Bu çekirdekler, yüksek bant genişlikli bellek (HBM) ihtiyacını azaltarak işlem süreçlerini hızlandırıyor.

- İki çiplet, 1 numaralı çipletler arası (ICI) bağlantıdan 6 kat daha hızlı bir yonga-yonga (D2D) ara bağlantısı ile birbirine bağlanıyor.

- Tek bir TPU rafı, her bir çipe 1.2 TB/s çift yönlü ICI bant genişliği sağlayan ICI aracılığıyla birbirine bağlı 64 çipten oluşuyor. Bu temel 64 çip yapılandırmasına 'küp' adı veriliyor.

- Birden çok küp, bir Optik Devre Anahtarı (OCS) ağı kullanılarak birbirine bağlanarak 9.216 çip ve 144 küpten oluşan bir 'süperpod' oluşturuyor.

Google'ın yeni TPU'su performansıyla dikkat çekiyor. Özellikle çıkarım (inferencing) görevlerinde NVIDIA'nın GPU'larıyla oldukça rekabetçi bir performans sergiliyor. Ayrıca, yaklaşan TPU'nun, NVIDIA'nın en yeni GPU'larıyla neredeyse aynı performansı sunarken daha düşük bir toplam sahip olma maliyetine (TCO) sahip olduğu belirtiliyor.

Google'ın TPU v7 Ironwood'unda MediaTek'in Katkısı

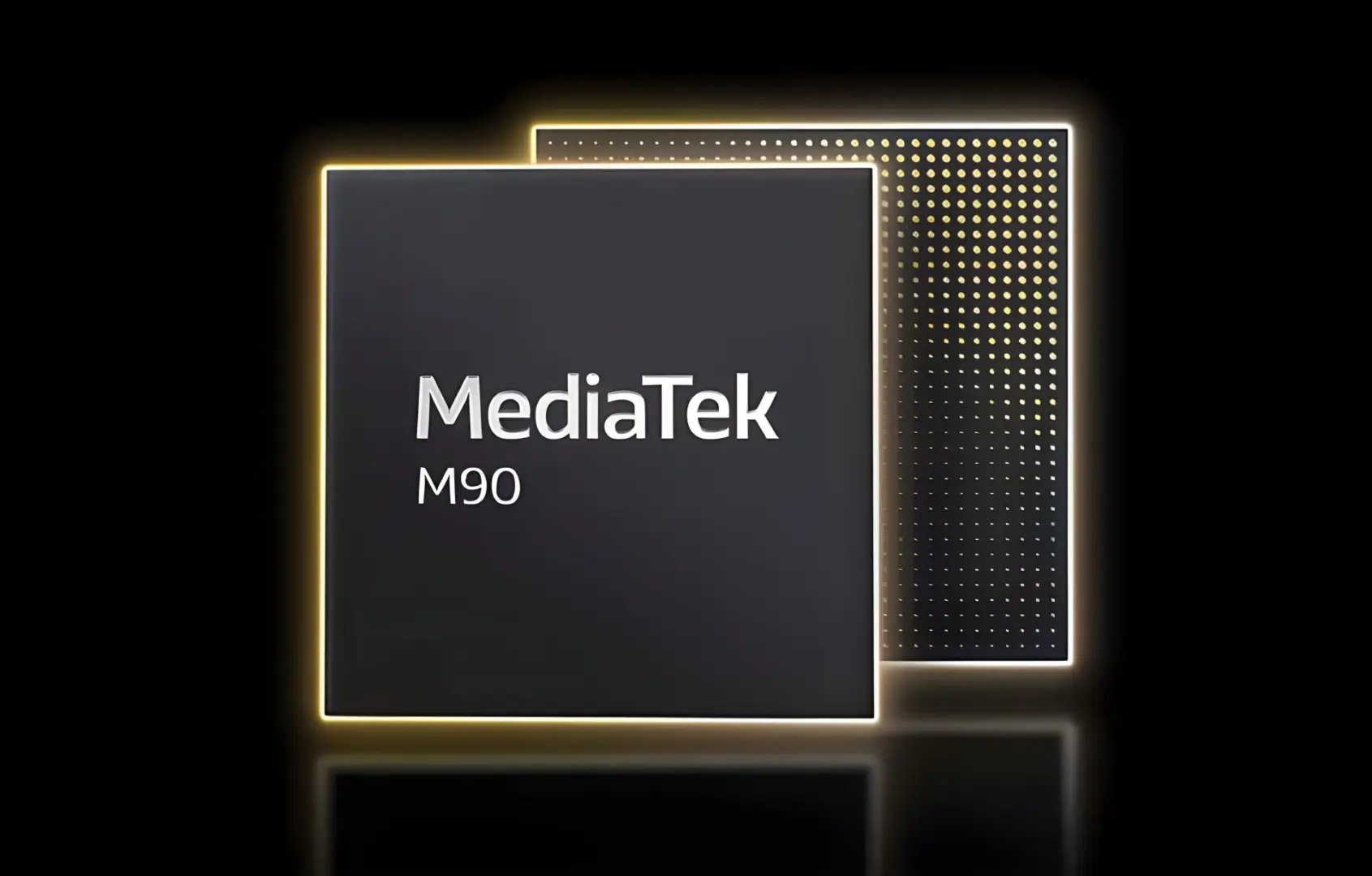

MediaTek, Google'ın TPU v7 Ironwood'unun tasarımında önemli bir rol oynadı. Elde edilen bu deneyim, şirketin önümüzdeki Dimensity 9600 yonga setini çok daha verimli hale getirecek. Mart 2025'te ortaya çıkan raporlara göre, Google, Ironwood'un giriş/çıkış (I/O) modüllerini tasarlaması için MediaTek'e görev verdi. Bu, işlemci ve çevre birimleri arasındaki iletişimi kolaylaştırmayı amaçlıyor. Bu durum, Google'ın son yıllardaki stratejisinden bir ayrım anlamına geliyor; zira şirket daha önce yeni nesil TPU'larını Broadcom ile yakın bir işbirliği içinde tasarlıyordu.

MediaTek'in Google TPU v7 Ironwood Üzerindeki Çalışmaları, Daha Verimli Bir Dimensity 9600 Chip İçin Beklentileri Nasıl Artırıyor?

Özel entegre devreler (ASIC) ve Dimensity 9600 gibi mobil uygulama işlemcileri (AP) doğası gereği farklıdır. Bu, MediaTek'in tüm deneyimini Dimensity 9600 için doğrudan kullanılamayacağı anlamına gelir. Bununla birlikte, şirket aşağıdaki iyileştirmelerle önemli adımlar atabilir:

- Dimensity 9600 yonga seti için daha verimli bir güç kapama (power gating) stratejisi geliştirmek. Bu, uygulama işlemcisinin kullanılmadığı zamanlarda belirli I/O bloklarını daha agresif bir şekilde kapatmasına olanak tanır.

- Dimensity 9600'ün voltaj ölçeklendirmesini iyileştirmek. Bu, uygulama işlemcisinin en verimli voltaj miktarını tüketmesini sağlayarak çipin güç tüketimi metriklerini iyileştirir.

- Önceki nesil çipin pil ömrünü iyileştirmek ve daha agresif güç bütçeleri için mücadele etmek üzere mevcut saat kapama (clock gating) stratejilerini ayarlamak.

MediaTek'in kendi yapay zeka yongaları üzerinde de çalıştığı ve TPU deneyiminin bu alanda daha fazla relevans göstereceği bildiriliyor. Bununla birlikte, yukarıda belirtilen ayarlamaların uygulanmasıyla mobil uygulama işlemcileri de fayda sağlayabilir. Özellikle MediaTek'in mobil uygulama işlemcisi mimarisinde verimlilik çekirdeklerinden (efficiency cores) vazgeçtiği düşünüldüğünde, bu iyileştirmeler büyük önem taşıyor.