AMD, yeni nesil Zen 6 işlemcilerinde çip içi iletişim teknolojisinde büyük bir yeniliğe hazırlanıyor. Bu yeniliğin ilk işaretleri ise Strix Halo APU'larında görülmeye başlandı.

Teknoloji dünyasında, işlemci performansını artırmak için genellikle gelişmiş üretim süreçleri, yenilikçi çiplet tasarımları ve benzeri yöntemlere başvurulur. Ancak, çipden çipe (D2D) iletişim teknolojisi konusunda AMD, Zen 2'den bu yana aynı yaklaşımı sürdürüyordu. Fakat önümüzdeki Zen 6 işlemcilerle bu durumun değişmesi bekleniyor. İlginç bir şekilde, bu yeni iletişim yaklaşımının izleri Strix Halo APU'larında şimdiden kendini gösteriyor.

Mevcut iletişim sisteminde, AMD, işlemci çekirdeklerinin (CCD) kenar çipleri arasındaki iletişimi sağlamak için 'SERDES PHYs' adı verilen bir teknolojiden faydalanıyor. Bu teknoloji, yüksek hızlı seri veri hatları aracılığıyla farklı çipleri birbirine bağlıyor. SERDES, seri hale getirici/paralel hale getirici anlamına gelir ve her bir CCD'den gelen paralel veriyi seri bit akışlarına dönüştürerek paket üzerinden iletmek için kullanılır. Çünkü geleneksel alt katmanlarda çipsetleri birbirine yüzlerce bakır tel ile bağlamak pratik değildir.

Diğer uçta ise, seri hale getirici bu seri bit akışlarını diğer taraftaki ağa geri dönüştürür. SERDES'in neden verimsiz bir yaklaşım olabileceğini düşündüyseniz, haklısınız. Seri hale getirme/paralel hale getirme işleminin getirdiği ek yük, saat sinyali kurtarma, eşitleme ve kodlama/kod çözme gibi işlemler için enerji tüketir. İkinci olarak, veri akışlarının dönüştürülmesi, çipden çipe iletişimde gecikmeye de neden olur ki bu da mevcut yöntemin bir dezavantajıdır.

SERDES yaklaşımı, D2D iletişiminin sınırlı sayıda 'geleneksel' çip setine indirgendiği zamanlar için yeterliydi. Ancak, yeni sinir işlem birimlerinin (NPU) eklenmesiyle birlikte AMD gibi firmaların belleğe ve CCD'lere kesintisiz, düşük ek yüklü bir bant genişliğine ihtiyaç duyması gerekiyordu. İşte Strix Halo ile AMD, Zen 6 çip setlerinin iletişim kurma şeklini kökten değiştirdi. Bu, TSMC'nin InFO-oS (Substrat Üzerinde Entegre Fan-Out) teknolojisi ve bir yeniden dağıtım katmanı (RDL) ile birlikte gerçekleştiriliyor.

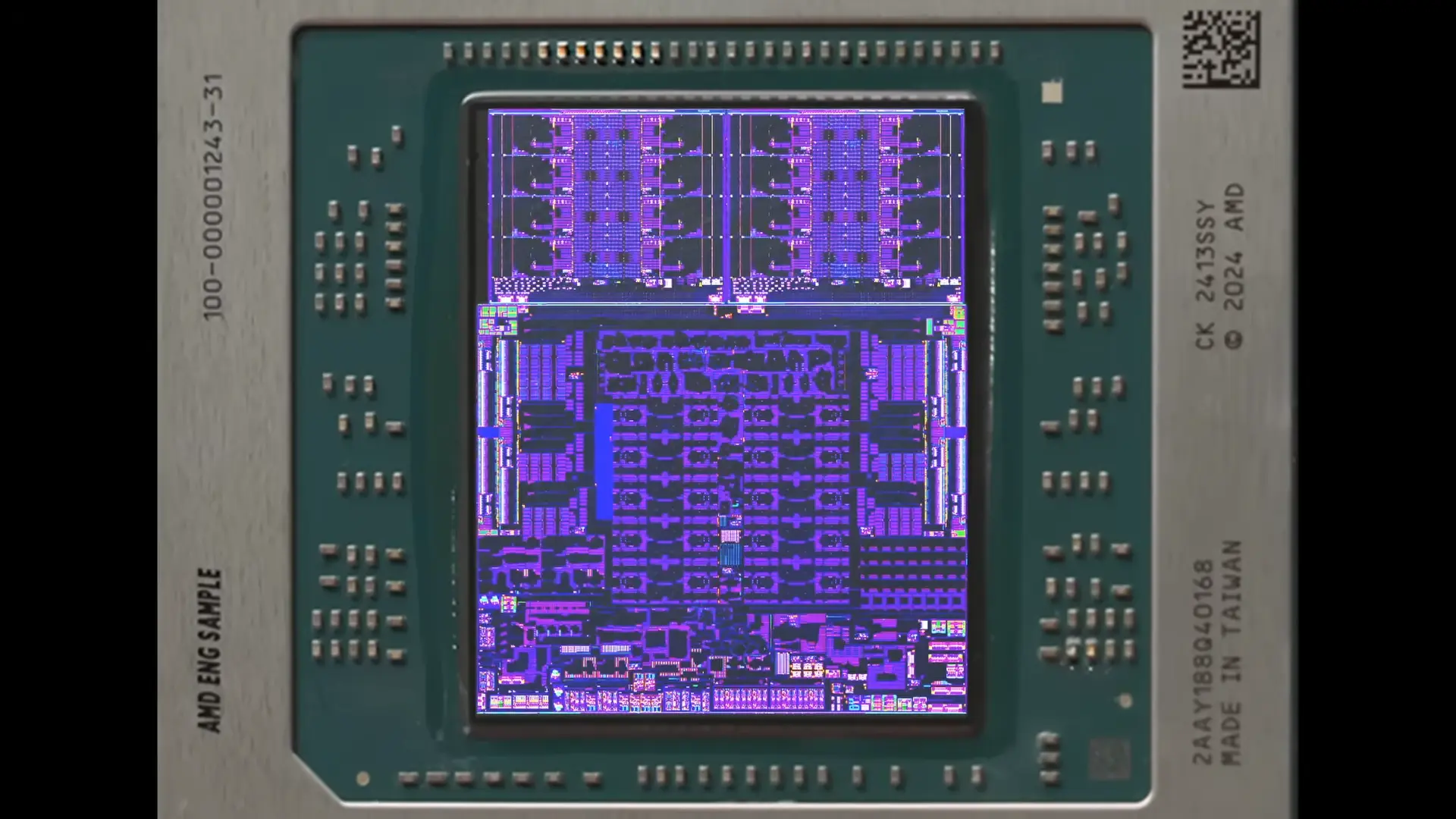

Veri akışlarını dönüştürmenin getirdiği ek yükü ortadan kaldırmak için AMD, Strix Halo'da çip setleri arasında, RDL'den yapılmış alt katmandaki 'interposer' üzerinde yer alan kısa ve ince paralel kablolar kullandı. InFO-oS aracılığıyla üretici, silikon çip setleri ile organik alt katman arasındaki kabloları yerleştirdi ve artık CPU ağı geniş paralel portlar üzerinden iletişim kuruyor. Bu yeni yaklaşımın nasıl keşfedildiği sorulursa, Strix Halo'nun küçük pedlerden oluşan dikdörtgen bir alana sahip olması, 'fan-out' uygulamasının klasik bir temsilidir ve büyük 'SERDES' bloğu kaldırılmıştır.

Yeni yaklaşımla birlikte, seri hale getirme/paralel hale getirme işlemi ortadan kalktığı için hem güç hem de gecikme gereksinimleri azalıyor. Daha da önemlisi, CPU ağı üzerindeki port sayısını artırarak genel bant genişliği ölçeklenebilirliği sağlanıyor. Ancak, fan-out yaklaşımının, özellikle çok katmanlı RDL'lerin tasarım karmaşıklığı gibi zorlukları da beraberinde getirdiğini belirtmek gerekir. Ayrıca, alt çip alanı fan-out kablolarıyla dolduğundan, yönlendirme önceliklerinin de değişmesi gerekiyor.

Her durumda, AMD'nin Strix Halo ile D2D iletişim alanında getirdiği yenilikleri görmek heyecan verici ve bu yaklaşımın Zen 6 işlemcilerle de devam etmesi bekleniyor.