Günümüz işlemcilerini genellikle küçük bileşenler olarak düşünsek de, dünyanın en büyük çip üreticilerinden TSMC, standart modellere göre 40 kata kadar daha yüksek performans sunabilecek devasa işlemciler üzerinde çalışıyor. Çoklu çip birimlerinden oluşacak bu yeni nesil çipler, CD kutusu boyutunu aşan paketleme teknolojileriyle üretilecek.

Yüksek performanslı hesaplama (HPC) ve yapay zeka (YZ) gibi alanlarda artan ihtiyaçlar, işlemcilerin daha fazla işlem gücü barındırmasını gerektiriyor. Mevcut işlemcilerde de çoklu çip birimi tasarımları kullanılsa da, TSMC bu sınırı daha da zorluyor.

TSMC'den Dev Adım: 3DFabric Yol Haritası

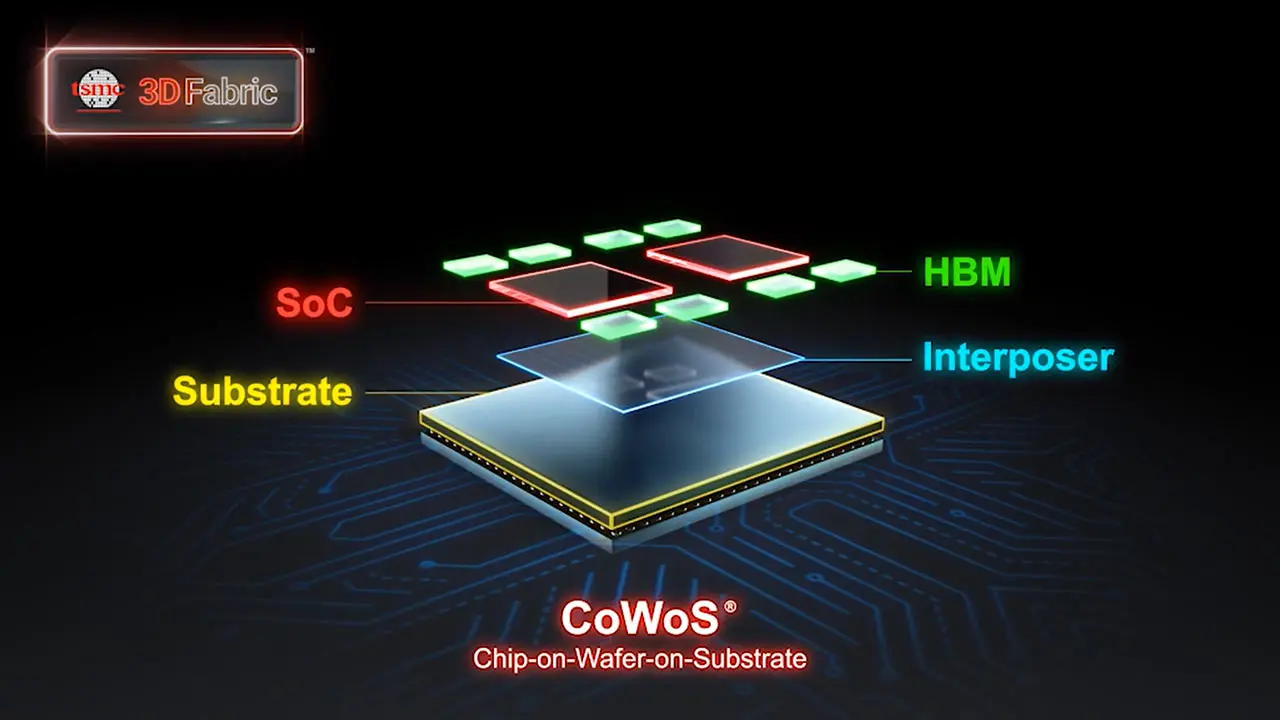

TSMC, bu talebi karşılamak amacıyla gelişmiş paketleme teknolojilerini (özellikle CoWoS adı verilen yöntemini) büyütüyor. Şirketin Kuzey Amerika Teknoloji Sempozyumu'nda duyurduğu yeni 3DFabric yol haritası, çip paketlemede kullanılan ara katmanların (interposer) boyutlarını mevcut limitlerin çok ötesine taşımayı hedefliyor.

Halihazırda kullanılan CoWoS teknolojisi, 3.3 kat foto maske boyutuna kadar ara katmanları destekliyor. Ancak gelecekteki uygulamalar için bu yeterli değil.

TSMC, önümüzdeki yıl veya biraz daha geç bir zamanda, CoWoS-L paketleme teknolojisinin yeni neslini tanıtmayı planlıyor. Bu teknoloji, standart çip üretim şablonunun yaklaşık 5.5 katı büyüklüğünde, 4.719 mm²'ye kadar ara katmanları destekleyecek. Bu sayede 12 adede kadar yüksek bant genişlikli belleği (HBM) ve daha büyük bir tabanı barındırabilecek. Bu çözümlerin mevcut tasarımlara göre üç buçuk kattan fazla hesaplama performansı sunması bekleniyor.

Ancak TSMC'nin hedefleri bununla sınırlı değil. Şirket, ara katman boyutunu 7.885 mm²'ye, yani standart şablon boyutunun yaklaşık 9.5 katına çıkarmayı planlıyor. Bu devasa çipler, CD kutusundan bile büyük, 120×150 mm'lik bir taban üzerinde yer alacak. Bu paketler; 3D olarak istiflenmiş sistem-üzerinde-çipler (SoIC), 12 adede kadar HBM4 bellek yığını ve ek giriş/çıkış birimlerini barındırabilecek.

Güç ve Soğutma Zorlukları

Bu kadar büyük ve performanslı işlemciler, kilowatt seviyesinde güç gereksinimine sahip olacak. Bu güç ihtiyacını karşılamak, hem çip geliştiricileri hem de sunucu üreticileri için büyük bir zorluk teşkil ediyor. TSMC, bu sorunu sistem düzeyinde çözmek için de adımlar atıyor.

Şirket, CoWoS-L paketlerine doğrudan güç yönetimi entegre devreleri (PMIC) ve yonga üzerinde indüktörler yerleştirmeyi hedefliyor. Bu sayede güç kaynakları ile işlemci birimleri arasındaki mesafenin azaltılması ve güç dağıtımının daha verimli hale getirilmesi amaçlanıyor. TSMC, bu entegre PMIC'lerin voltaj kontrolünü kolayca yapabildiğini ve geleneksel yöntemlere göre beş kata kadar daha yüksek güç dağıtım yoğunluğu sunduğunu belirtiyor.

Ayrıca, ara katmana veya silikon tabana gömülü kapasitörler, voltaj dalgalanmalarını filtreleyerek güç kararlılığını artıracak. Bu gelişmeler, karmaşık çoklu çekirdekli veya çoklu çipli tasarımlarda güç verimliliği ve kararlı çalışma için kritik öneme sahip.

TSMC'nin yaklaşımı, gücün silikona dağıtımının yalnızca bir bileşen özelliği olarak değil, tüm sistem (silikon, paketleme ve sistem tasarımı) kapsamında optimize edilmesi gerektiği yönündeki değişimi yansıtıyor.

Boyutlar ve Soğutma İhtiyacı

Daha büyük ara katman boyutları, sistem tasarımını da etkileyecek. Planlanan 100×100 mm ve özellikle 120×150 mm'lik tabanlar, mevcut endüstri standartlarını (form faktörleri) aşacak, bu da yeni modül ve kart tasarımlarını gerektirecek.

Fiziksel sınırlamaların ve güç tüketiminin yanı sıra, bu devasa çoklu çip paketleri muazzam miktarda ısı üretecek. Donanım üreticileri, bu ısı yükünü yönetmek için doğrudan sıvı soğutma ve daldırma soğutma gibi gelişmiş yöntemleri şimdiden araştırıyor. Ancak TSMC, bu soğutma sorununu çip seviyesinde tek başına çözemeyeceğini belirtiyor.